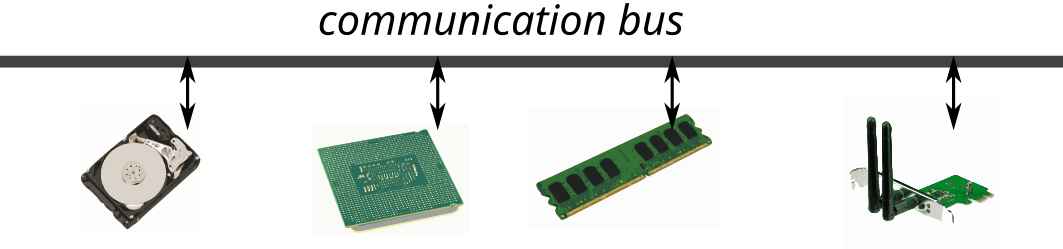

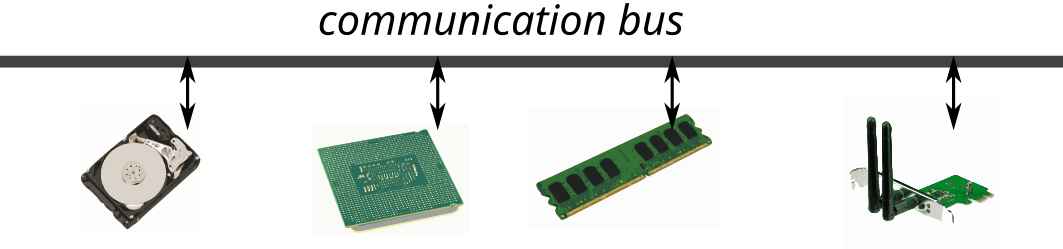

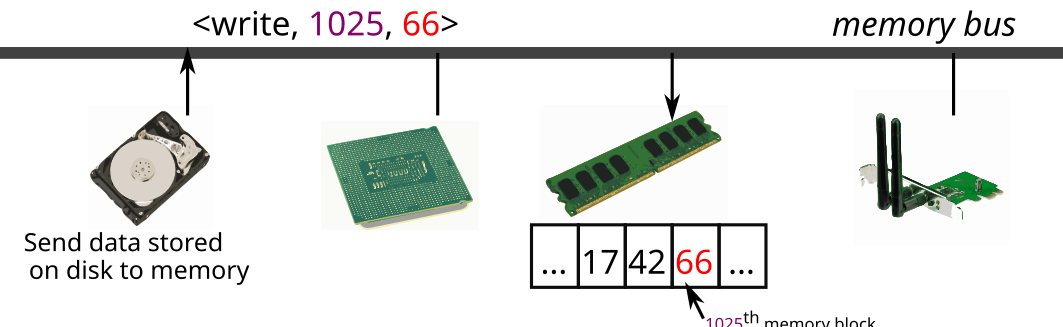

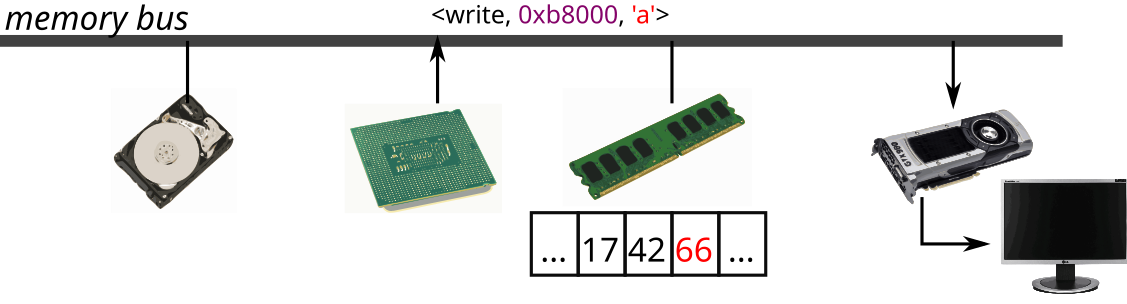

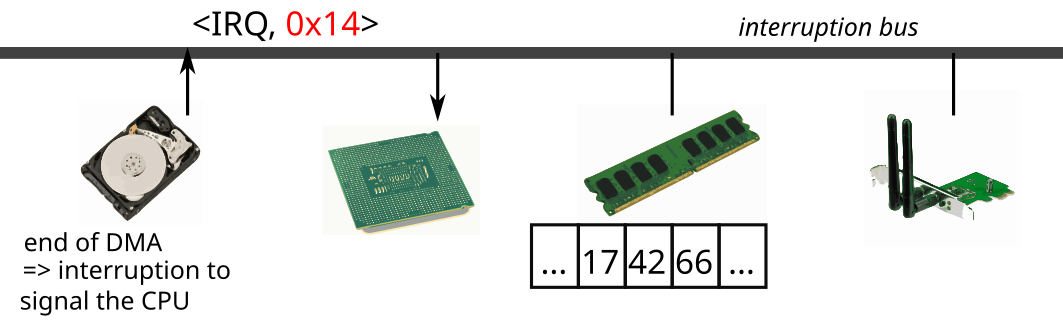

Devices use the memory bus for reads/writes

The DMA controller manages the transfer between peripherals or memory

\(\rightarrow\) The processor can execute instructions during an I/O

Processors use memory bus to access devices

Device memory is mapped in memory

Request / response protocol, special instructions

in/out

stvec

0X14 signals a data block is

available0x14:

0x20x2

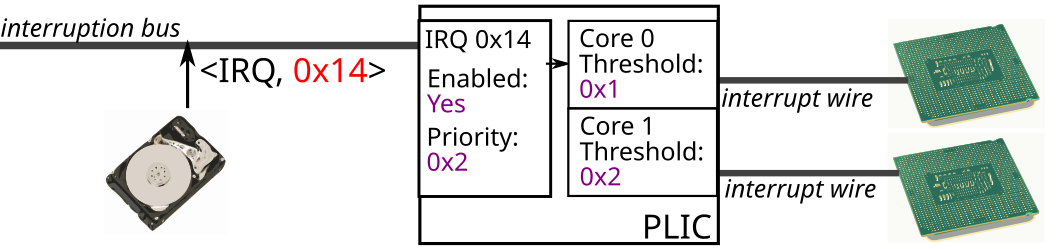

In Non Uniform Memory Access architectures (NUMA), a device is linked

to only one NUMA node. On RISC-V architectures, this means

a device is linked to only one PLIC, as there is one PLIC per NUMA node.

So only a processor from this NUMA node can serve interrupts from this

device.

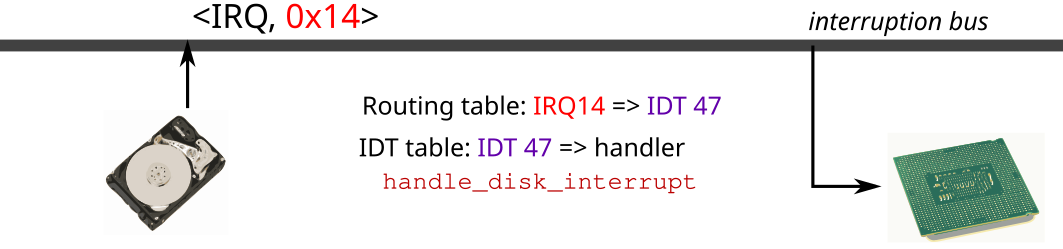

x86 architectureOn x86, interrupt routing goes through two tables

configured by the kernel:

Two tables allow more flexibility than a single table which

associates an IRQ number directly with a manager. This is different from

RISC-V architecture where there can only be one interrupt

handler, that must check the kind of the interrupt to serve it (e.g., a

device interrupt, a timer interrupt, etc.).

Example of routing:

A device sends an IRQ (for example

0x14)

The routing table associates IRQ14

with IDT47

The IDT table indicates that IDT47

is managed by the function handle_disk_interrupt

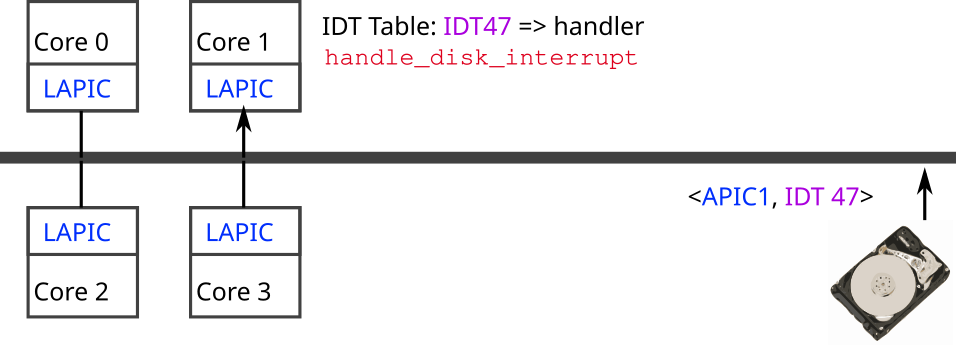

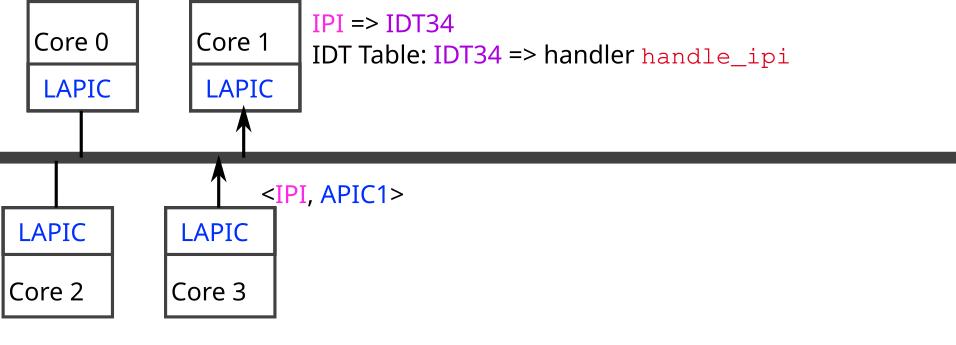

This is with only one processor; on multicore x86

systems:

XAPIC protocol on pentium (x2APIC since Intel Core processors)

Each core has a number called APIC number (Advanced Programmable Interrupt Controller)

Each core handles interrupts via its LAPIC (local APIC)

An IOAPIC routes an interrupt to a given LAPIC

SIE (Supervisor Interrupts

Enable) in register SSTATUS

RISC-V architecturesThe PLIC (usually an APLIC, Advanced PLIC) remains used by devices that do not (need to) support MSI. When the platform supports MSIs, the APLIC converts wired (i.e., non message signaled) interrupts into MSIs. This is configured by the OS, as if they were direct MSIs from external devices.

x86On x86 systems, MSIs work roughly the same:

x86

architectures

The interrupt handler (the function addressed by register

stvec) is also called when system calls

and exceptions occur

ecall, which triggers an interrupt of this

type0x5stvec points to the unique entrypoint

into the kernel:

On x86 systems, the IDT table is used for every possible

interruption:

int 0x64

simply generates the interrupt IDT 0x64IDT 0x00, an

access illicit memory (SIGSEGV) the interrupt

IDT 0x0e etc.The IDT table is therefore the table that contains all of the entry points to the kernel:

Jiffies: global time source to update the date

Tick: core-local time source used for scheduling